# MIC24045

# I<sup>2</sup>C Programmable, 4.5V-19V Input, 5A Step-Down Converter

#### **Features**

- 4.5V to 19V Input Voltage Range

- · 5A (maximum) Output Current

- I<sup>2</sup>C Programmable Output Voltage:

- 0.64V to 5.25V in 5 mV, 10 mV, 30 mV and 50 mV steps

- High Efficiency (>95%)

- I<sup>2</sup>C Programmability of:

- Soft-Start: 0.16, 0.38, 0.76 and 1.5V/ms ramp rates

- Switching Frequency: 310 kHz, 400 kHz, 500 kHz, 570 kHz, 660 kHz, 780 kHz, 1 MHz, 1.2 MHz

- Current Limits for 2A, 3A, 4A and 5A loads

- Output Voltage Margining: -5%, +5%

- Start-up delays: 0 ms to 10 ms

- ±1% Output Voltage Accuracy Over Temperature (0.64V to 1.95V)

- · Supports Safe Start-Up with Pre-Biased Output

- Extensive Diagnostics through I<sup>2</sup>C Interface

#### **Applications**

- Servers, Data Storage, Routers and Base Stations

- · FPGAs, DSP and Low-Voltage ASIC Power

#### **General Description**

The MIC24045 is an I<sup>2</sup>C-programmable, high-efficiency, wide input range, 5A synchronous step-down regulator. The MIC24045 is perfectly suited for multiple voltage rail application environments, typically found in computing and telecommunication systems. In the MIC24045 various parameters can be programmed via I<sup>2</sup>C, such as output voltage, switching frequency, soft-start slope, margining, current limit values and start-up delays. The wide switching frequency adjustment range, valley current-mode control technique, high-performance error amplifier and external compensation allow for the best trade-offs between high efficiency and the smallest possible solution size.

The MIC24045 supports extensive diagnostics and status information through I<sup>2</sup>C.

The MIC24045 pinout is compatible with the MIC24046 pin-strapping programmable regulator pinout, such that I<sup>2</sup>C-based implementations can be easily converted into pin-programmable ones.

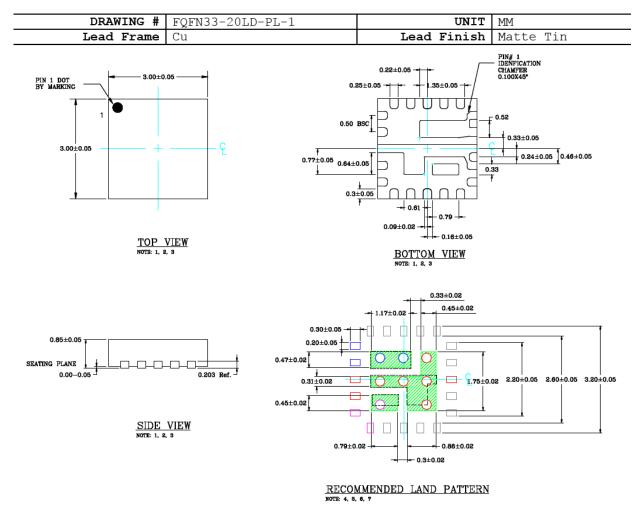

The MIC24045 is available in a thermally-efficient, space-saving 20-pin 3 mm x 3 mm FQFN package, with an operating junction temperature range from -40°C to +125°C.

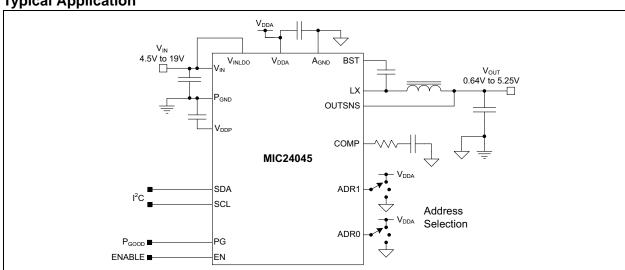

#### **Typical Application**

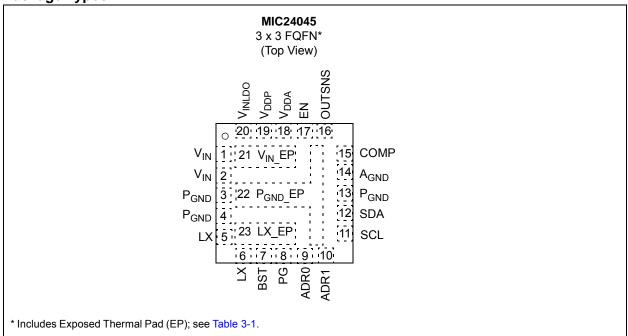

#### **Package Types**

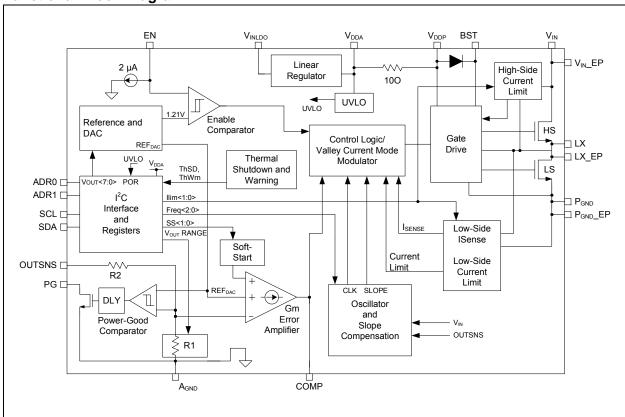

#### **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings †**

| V <sub>IN</sub> , V <sub>INLDO</sub> , V <sub>LX</sub> to A <sub>GND</sub>  | -0.3V to +20V                      |

|-----------------------------------------------------------------------------|------------------------------------|

| V <sub>DDP</sub> , V <sub>DDA</sub> to A <sub>GND</sub>                     | -0.3V to +6V                       |

| V <sub>INLDO</sub> to V <sub>DDA</sub>                                      |                                    |

| V <sub>DDP</sub> to V <sub>DDA</sub>                                        | -0.3V to +0.3V                     |

| V <sub>ADRx</sub> , V <sub>SDA</sub> , V <sub>SCL</sub> to A <sub>GND</sub> | -0.3V to +6V                       |

| V <sub>BST</sub> to V <sub>LX</sub>                                         | -0.3V to +6V                       |

| V <sub>BST</sub> to A <sub>GND</sub>                                        | -0.3V to +26V                      |

| V <sub>EN</sub> to A <sub>GND</sub>                                         | 0.3V to V <sub>DDA</sub> +0.3V,+6V |

| V <sub>PG</sub> to A <sub>GND</sub>                                         | -0.3V to +6V                       |

| V <sub>COMP</sub> , V <sub>OUTSNS</sub> to A <sub>GND</sub>                 | 0.3V to V <sub>DDA</sub> +0.3V,+6V |

| A <sub>GND</sub> to P <sub>GND</sub>                                        | -0.3V to +0.3V                     |

| Junction Temperature                                                        | +150°C                             |

| Storage Temperature (T <sub>S</sub> )                                       | 65°C to +150°C                     |

| Lead Temperature (soldering, 10s)                                           | 260°C                              |

| ESD Rating <sup>(1)</sup>                                                   |                                    |

| HBM                                                                         | 2000V                              |

| CDM                                                                         | 2000V                              |

**† Notice:** Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

**Note 1:** Devices are ESD sensitive. Handling precautions recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

### Operating Ratings<sup>(1)</sup>

| Supply Voltage (V <sub>IN,</sub> V <sub>INLDO</sub> )                                                            | 4.5V to 19V            |

|------------------------------------------------------------------------------------------------------------------|------------------------|

| Externally Applied Analog and Drivers Supply Voltage (V <sub>INLDO</sub> = V <sub>DDA</sub> = V <sub>DDP</sub> ) | 4.5V to 5.5V           |

| Enable Voltage (V <sub>EN</sub> )                                                                                | 0V to V <sub>DDA</sub> |

| Power-Good (PG) Pull-up Voltage (V <sub>PU_PG</sub> )                                                            | 0V to 5.5V             |

| Output Current                                                                                                   | 5A                     |

| Junction Temperature (T <sub>J</sub> )                                                                           | 40°C to +125°C         |

**Note 1:** The device is not ensured to function outside the operating range.

### **ELECTRICAL CHARACTERISTICS (Note 1)**

Electrical Specifications: unless otherwise specified,  $V_{IN}$  =  $V_{INLDO}$  = 12V;  $C_{VDDA}$  = 2.2 μF,  $C_{VDDP}$  = 2.2 μF,  $T_A$  = +25°C. Boldface values indicate -40°C ≤  $T_J$  ≤ +125°C.

| Parameter                                                 | Symbol                | Min. | Тур. | Max. | Units | Test Conditions                                                                                       |

|-----------------------------------------------------------|-----------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------|

| V <sub>IN</sub> Supply                                    |                       |      |      |      |       |                                                                                                       |

| Input Range                                               | V <sub>IN</sub>       | 4.5  | _    | 19   | V     |                                                                                                       |

| Disable Current                                           | I <sub>VINQ</sub>     | _    | 0.2  | 2    | μA    | EN = 0V                                                                                               |

| Disable Current                                           | I <sub>VINLDOQ</sub>  | _    | 0.6  | 1    | mA    | EN = 0V                                                                                               |

| Operating Current                                         | I <sub>VINOp</sub>    | _    | 0.3  | 0.5  | mA    | EN > 1.28V, ILIM<1:0> = 00,<br>OUTSNS = 1.15 x $V_{OUT(NOM)}$ ,<br>no switching, $T_A = T_J = +25$ °C |

| Operating Current                                         | I <sub>VINLDOOp</sub> | _    | 4.5  | 7    | mA    | EN > 1.28V,<br>OUTSNS = 1.15 x $V_{OUT(NOM)}$ ,<br>no switching, $T_A = T_J = +25$ °C                 |

| V <sub>DDA</sub> 5V Supply                                |                       |      |      |      |       |                                                                                                       |

| Operating Voltage                                         | $V_{DDA}$             | 4.8  | 5.1  | 5.4  | V     | $I_{VDDA} = 0$ mA to 10 mA                                                                            |

| Dropout Operation                                         |                       | 3.6  | 4.2  |      | V     | $V_{INLDO}$ = 4.5V, $I_{VDDA}$ = 10 mA                                                                |

| V <sub>DDA</sub> Undervoltage Lockout                     |                       |      |      |      |       |                                                                                                       |

| V <sub>DDA</sub> UVLO Rising                              | UVLO_R                | 3.1  | 3.5  | 3.9  | V     | V <sub>DDA</sub> Rising, EN > 1.28V                                                                   |

| V <sub>DDA</sub> UVLO Falling                             | UVLO_F                | 2.87 | 3.2  | 3.45 | V     | V <sub>DDA</sub> Falling, EN > 1.28V                                                                  |

| V <sub>DDA</sub> UVLO Hysteresis                          | UVLO_H                |      | 300  | _    | mV    |                                                                                                       |

| EN Control                                                |                       |      |      |      |       |                                                                                                       |

| EN Rising Threshold                                       | EN_R                  | 1.14 | 1.21 | 1.28 | V     | Initiates power-stage operation                                                                       |

| EN Falling Threshold                                      | EN_F                  |      | 1.07 | _    | V     | Stops power-stage operation                                                                           |

| EN Hysteresis                                             | EN_H                  |      | 135  | _    | mV    |                                                                                                       |

| EN Pull-Down Current                                      | EN_I                  | 1    | 2    | 3    | μA    | $T_A = T_J = +25^{\circ}C$                                                                            |

| Switching Frequency                                       |                       |      |      |      |       |                                                                                                       |

| Programmable Frequency 0                                  | f <sub>s0</sub>       | 270  | 310  | 350  | kHz   |                                                                                                       |

| Programmable Frequency 1                                  | f <sub>s1</sub>       | 350  | 400  | 450  | kHz   |                                                                                                       |

| Programmable Frequency 2                                  | f <sub>s2</sub>       | 450  | 500  | 550  | kHz   |                                                                                                       |

| Programmable Frequency 3                                  | f <sub>s3</sub>       | 510  | 570  | 630  | kHz   |                                                                                                       |

| Programmable Frequency 4                                  | f <sub>s4</sub>       | 590  | 660  | 740  | kHz   |                                                                                                       |

| Programmable Frequency 5                                  | f <sub>s5</sub>       | 680  | 780  | 880  | kHz   |                                                                                                       |

| Programmable Frequency 6                                  | f <sub>s6</sub>       | 850  | 970  | 1100 | kHz   |                                                                                                       |

| Programmable Frequency 7                                  | f <sub>s7</sub>       | 1050 | 1200 | 1350 | kHz   |                                                                                                       |

| Overcurrent Protection                                    |                       |      |      |      |       |                                                                                                       |

| HS Current Limit 0                                        | I <sub>LIM_HS0</sub>  | 4.0  | 4.7  | 6.5  | Α     |                                                                                                       |

| HS Current Limit 1                                        | I <sub>LIM_HS1</sub>  | 5.4  | 6.2  | 7.6  | Α     |                                                                                                       |

| HS Current Limit 2                                        | I <sub>LIM_HS2</sub>  | 7.6  | 8.6  | 10.6 | Α     |                                                                                                       |

| HS Current Limit 3                                        | I <sub>LIM_HS3</sub>  | 8.2  | 9.4  | 12.0 | Α     |                                                                                                       |

| High Side FET Current-Limit<br>Leading Edge-Blanking Time | LEB                   | _    | 108  | _    | ns    |                                                                                                       |

| LS Current Limit 0                                        | I <sub>LIM_LS0</sub>  | 2.0  | 3.25 | 5.0  | Α     |                                                                                                       |

| LS Current Limit 1                                        | I <sub>LIM_LS1</sub>  | 3.0  | 4.3  | 6.0  | Α     |                                                                                                       |

| LS Current Limit 2                                        | I <sub>LIM_LS2</sub>  | 4.0  | 5.6  | 7.5  | Α     |                                                                                                       |

|                                                           | LIIVI_LO2             |      | l    | l    | 1     | 1                                                                                                     |

Note 1: Specification for packaged product only.

### **ELECTRICAL CHARACTERISTICS (Note 1)**

**Electrical Specifications:** unless otherwise specified,  $V_{IN}$  =  $V_{INLDO}$  = 12V;  $C_{VDDA}$  = 2.2 μF,  $C_{VDDP}$  = 2.2 μF,  $T_A$  = +25°C. **Boldface** values indicate -40°C ≤  $T_J$  ≤ +125°C.

| Parameter                                    | Symbol                 | Min. | Тур.             | Max. | Units           | Test Conditions                                                                                                                                                                                                                                         |

|----------------------------------------------|------------------------|------|------------------|------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LS Current Limit 3                           | I <sub>LIM_LS3</sub>   | 5.0  | 6.2              | 8.5  | Α               |                                                                                                                                                                                                                                                         |

| OC Events Count for Hiccup                   | IN <sub>HICC_DE</sub>  |      | 15               | _    | Clock<br>Cycles | Number of subsequent cycles in current limit before entering hiccup overload protection.                                                                                                                                                                |

| Hiccup Wait Time                             | t <sub>HICC_WAIT</sub> | _    | 13.5V/<br>SS_SRx | _    | ms              | Duration of the high-Z state on LX before new soft-start. SS_SRx = SS_SR0, SS_SR1, SS_SR2, SS_SR3                                                                                                                                                       |

| Power Switches                               |                        |      |                  |      |                 |                                                                                                                                                                                                                                                         |

| Low Side FET ON Resistance                   | R <sub>LS</sub>        | _    | 16               | 21   | mΩ              | $V_{IN} = V_{INLDO} = V_{DDP} = V_{DDA} = 5V,$<br>$V_{BST}V_{LX} = 5V, T_A = T_J = +25^{\circ}C$                                                                                                                                                        |

| High Side FET ON Resistance                  | R <sub>HS</sub>        | _    | 38               | 50   | mΩ              | $V_{IN} = V_{INLDO} = V_{DDP} = V_{DDA} = 5V,$<br>$V_{BST}V_{LX} = 5V, T_A = T_J = +25^{\circ}C$                                                                                                                                                        |

| Pulse-Width Modulation (PWM                  | И)                     |      |                  |      |                 |                                                                                                                                                                                                                                                         |

| Minimum LX ON Time                           | T <sub>ON(MIN)</sub>   |      | 26               | _    | ns              | $T_A = T_J = +25$ °C                                                                                                                                                                                                                                    |

| Minimum LX OFF time                          | T <sub>OFF(MIN)</sub>  | 90   | 145              | 190  | ns              | $\begin{aligned} & V_{\text{IN}} = V_{\text{INLDO}} = V_{\text{DDA}} = 5\text{V}, \\ & V_{\text{OUTSNS}} = 3\text{V}, 400 \text{ kHz setting}, \\ & V_{\text{OUT}} = 3.3\text{V}, \\ & T_{\text{A}} = T_{\text{J}} = +25^{\circ}\text{C} \end{aligned}$ |

| Minimum Duty Cycle                           | D <sub>MIN</sub>       | _    | 0                | _    | %               | V <sub>OUTSNS</sub> > 1.1 x V <sub>OUT(NOM)</sub>                                                                                                                                                                                                       |

| Gm Error Amplifier                           |                        |      |                  |      |                 |                                                                                                                                                                                                                                                         |

| Error-Amplifier<br>Transconductance          | Gm <sub>EA</sub>       | _    | 1.4              | _    | mS              |                                                                                                                                                                                                                                                         |

| Error-Amplifier DC Gain                      | A <sub>EA</sub>        | _    | 50000            | _    | V/V             |                                                                                                                                                                                                                                                         |

| Error-Amplifier Source Current               | I <sub>SR</sub>        | _    | 400              | _    | μA              |                                                                                                                                                                                                                                                         |

| Error-Amplifier Sink Current                 | I <sub>SNK</sub>       | _    | 400              | _    | μA              |                                                                                                                                                                                                                                                         |

| COMP Output Swing High                       | COMP_H                 | _    | 2.5              | _    | V               |                                                                                                                                                                                                                                                         |

| COMP Output Swing Low                        | COMP_L                 | _    | 8.0              | _    | V               |                                                                                                                                                                                                                                                         |

| COMP-to-Inductor Current<br>Transconductance | Gm <sub>PS</sub>       | _    | 12.5             | _    | A/V             | V <sub>OUT</sub> = 1.2V, I <sub>OUT</sub> = 4A                                                                                                                                                                                                          |

| Output Voltage DC Accuracy                   |                        |      |                  |      |                 |                                                                                                                                                                                                                                                         |

| Minimum Programmable Output Voltage          | MinOut                 | _    | 0.64             | _    | V               |                                                                                                                                                                                                                                                         |

| Maximum Programmable Output Voltage          | MaxOut                 | _    | 5.25             | _    | V               |                                                                                                                                                                                                                                                         |

| LSB for range 0.640V to 1.280V               | LSB1                   | _    | 5                | _    | mV              |                                                                                                                                                                                                                                                         |

| LSB for range 1.290V to 1.950V               | LSB2                   |      | 10               |      | mV              |                                                                                                                                                                                                                                                         |

| LSB for range 1.980V to 3.42V                | LSB3                   |      | 30               |      | mV              |                                                                                                                                                                                                                                                         |

| LSB for range 4.75V to 5.25V                 | LSB4                   | _    | 50               | _    | mV              |                                                                                                                                                                                                                                                         |

| Output Voltage Accuracy for Ranges 1 and 2   | OutErr12               | -1   | _                | 1    | %               | $4.75V \le V_{IN} \le 19V,$<br>$V_{OUT} = 0.64V \text{ to } 1.95V$<br>$T_A = T_J = -40^{\circ}\text{C to } +125^{\circ}\text{C},$<br>$I_{OUT} = 0\text{A}$                                                                                              |

Note 1: Specification for packaged product only.

### **ELECTRICAL CHARACTERISTICS (Note 1)**

| Parameter                                 | Symbol                            | Min. | Тур. | Max. | Units | Test Conditions                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------|-----------------------------------|------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Output Voltage Accuracy for Range 3 and 4 | OutErr34                          | -1.5 | _    | 1.5  | %     | $\begin{array}{l} 4.75 \text{V} \leq \text{V}_{IN} \leq 19 \text{V for} \\ \text{V}_{OUT} = 1.98 \text{V to } 3.42 \text{V}, \\ 6 \text{V} \leq \text{V}_{IN} \leq 19 \text{V for } \text{V}_{OUT} = 4.75 \text{V to} \\ 5.25 \text{V}, \\ \text{T}_{A} = \text{T}_{J} = -40 ^{\circ} \text{C to } +125 ^{\circ} \text{C}, \\ \text{I}_{OUT} = 0 \text{A} \end{array}$ |

| Load Regulation                           | LoadReg                           | _    | 0.2  | _    | %     | $I_{OUT}$ = 0A to 5A, $V_{OUT}$ = 3.3V                                                                                                                                                                                                                                                                                                                                 |

| Line Regulation                           | LineReg                           | _    | 0.1  |      | %     | 6V < V <sub>IN</sub> < 19V, I <sub>OUT</sub> = 2A                                                                                                                                                                                                                                                                                                                      |

| Internal Soft-Start                       |                                   |      |      |      |       |                                                                                                                                                                                                                                                                                                                                                                        |

| Reference Soft-Start<br>Slew Rate 0       | SS_SR0                            | _    | 0.16 | _    | V/ms  | V <sub>OUT</sub> = 0.64 to 1.28V                                                                                                                                                                                                                                                                                                                                       |

| Reference Soft-Start<br>Slew Rate 1       | SS_SR1                            | _    | 0.38 |      | V/ms  | V <sub>OUT</sub> = 0.64 to 1.28V                                                                                                                                                                                                                                                                                                                                       |

| Reference Soft-Start<br>Slew Rate 2       | SS_SR2                            | _    | 0.76 |      | V/ms  | V <sub>OUT</sub> = 0.64 to 1.28V                                                                                                                                                                                                                                                                                                                                       |

| Reference Soft-Start<br>Slew Rate 3       | SS_SR3                            |      | 1.5  |      | V/ms  | V <sub>OUT</sub> = 0.64 to 1.28V                                                                                                                                                                                                                                                                                                                                       |

| Power Good (PG)                           |                                   |      |      |      |       |                                                                                                                                                                                                                                                                                                                                                                        |

| PG Low Voltage                            | PG_V <sub>OL</sub>                | _    | 0.18 | 0.4  | V     | I <sub>(PG)</sub> = 4 mA                                                                                                                                                                                                                                                                                                                                               |

| PG Leakage Current                        | PG_I <sub>LEAK</sub>              | -1   | 0.02 | 1    | μA    | V <sub>PG</sub> = 5V                                                                                                                                                                                                                                                                                                                                                   |

| PG Rise Threshold                         | PG_R                              | 90   | 92.5 | 95   | %     | V <sub>OUT</sub> Rising                                                                                                                                                                                                                                                                                                                                                |

| PG Fall Threshold                         | PG_F                              | 87.5 | 90   | 92.5 | %     | V <sub>OUT</sub> Falling                                                                                                                                                                                                                                                                                                                                               |

| PG Rise Delay                             | PG_R_DLY                          | _    | 0.45 | _    | ms    | V <sub>OUT</sub> Rising                                                                                                                                                                                                                                                                                                                                                |

| PG Fall Delay                             | PG_F_DLY                          | _    | 80   | _    | μs    | V <sub>OUT</sub> Falling                                                                                                                                                                                                                                                                                                                                               |

| Thermal Shutdown                          | 1 1                               |      | •    | 1    | 1     |                                                                                                                                                                                                                                                                                                                                                                        |

| Thermal Shutdown                          | T <sub>SHDN</sub>                 | _    | 160  |      | °C    |                                                                                                                                                                                                                                                                                                                                                                        |

| Thermal-Shutdown Hysteresis               | T <sub>SHDN_HYST</sub>            | _    | 25   | _    | °C    |                                                                                                                                                                                                                                                                                                                                                                        |

| Thermal Warning Threshold                 | T <sub>ThWrn</sub>                | _    | 120  | _    | °C    |                                                                                                                                                                                                                                                                                                                                                                        |

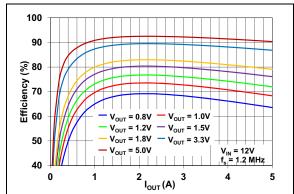

| Efficiency                                |                                   |      |      |      |       |                                                                                                                                                                                                                                                                                                                                                                        |

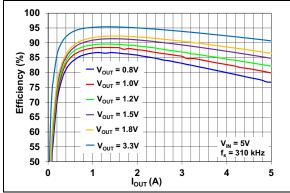

| Efficiency                                | η                                 | _    | 82.3 | _    | %     | $V_{IN}$ = 12V, $V_{OUT}$ = 0.9V, $I_{OUT}$ = 2A, $f_S$ = 400 kHz, L = 1.2 $\mu$ H, $T_A$ = +25°C                                                                                                                                                                                                                                                                      |

| I <sup>2</sup> C Interface                |                                   |      |      |      |       |                                                                                                                                                                                                                                                                                                                                                                        |

| SDA, SCL V <sub>IH</sub>                  | V <sub>IH</sub>                   | 2    | _    |      | V     | V <sub>DDA</sub> = 5V (levels are 3.3V compatible)                                                                                                                                                                                                                                                                                                                     |

| SDA, SCL V <sub>IL</sub>                  | V <sub>IL</sub>                   | _    | _    | 1    | V     | V <sub>DDA</sub> = 5V (levels are 3.3V compatible)                                                                                                                                                                                                                                                                                                                     |

| SDA, SCL Input High/Low<br>Current        | I <sub>IH</sub> , I <sub>IL</sub> | -1   | _    | 1    | μA    |                                                                                                                                                                                                                                                                                                                                                                        |

| SDA Output Low Voltage                    | V <sub>OL</sub>                   | _    | _    | 0.4  | V     | I <sub>SDA</sub> = 3 mA                                                                                                                                                                                                                                                                                                                                                |

Note 1: Specification for packaged product only.

### **TEMPERATURE SPECIFICATIONS**

**Electrical Specifications:** unless otherwise specified,  $V_{IN} = V_{INLDO} = 12V$ ;  $C_{VDDA} = 2.2 \mu F$ ,  $C_{VDDP} = 2.2 \mu F$ ,  $T_A = +25^{\circ}C$ .

**Boldface** values indicate  $-40^{\circ}$ C  $\leq$  T<sub>J</sub>  $\leq$  +125 $^{\circ}$ C.

| Parameters                        | Sym.              | Min. | Тур. | Max. | Units | Conditions |  |  |  |

|-----------------------------------|-------------------|------|------|------|-------|------------|--|--|--|

| Temperature Ranges                |                   |      |      |      |       |            |  |  |  |

| Junction Temperature              | $T_J$             | -40  | _    | +125 | °C    |            |  |  |  |

| Storage Temperature Range         | $T_A$             | -65  | _    | +150 | °C    |            |  |  |  |

| Package Thermal Resistances       |                   |      |      |      |       |            |  |  |  |

| Thermal Resistance, 20LD 3x3 FQFN | $\theta_{\sf JA}$ | _    | 29   | _    | °C/W  |            |  |  |  |

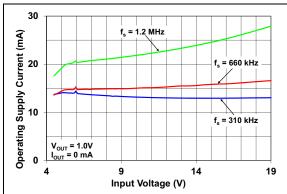

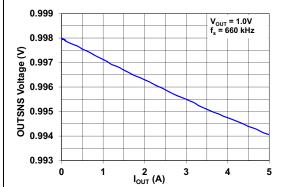

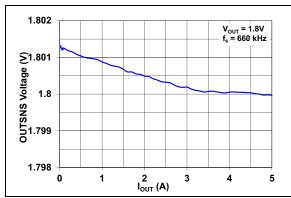

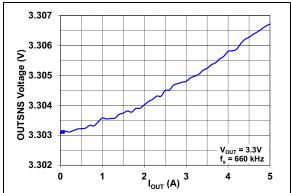

#### 2.0 TYPICAL CHARACTERISTIC CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: Operating Supply Current vs. Input Voltage, Switching.

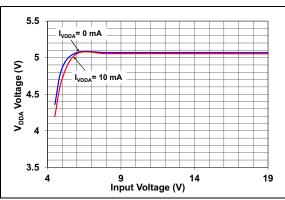

FIGURE 2-2: V<sub>DDA</sub> vs. Input Voltage.

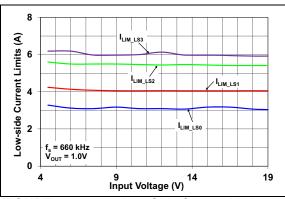

FIGURE 2-3: Low-Side Current Limits vs. Input Voltage.

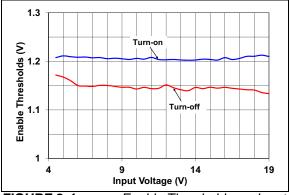

FIGURE 2-4: Enable Thresholds vs. Input Voltage.

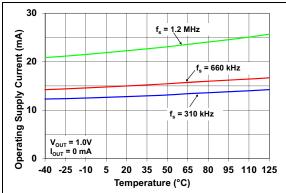

**FIGURE 2-5:** Operating Supply Current vs. Temperature, Switching.

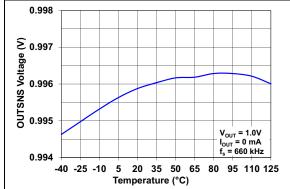

FIGURE 2-6: OUTSNS Voltage vs. Temperature.

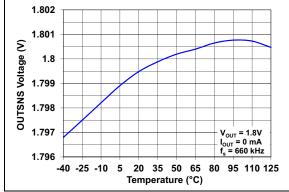

FIGURE 2-7: OUTSNS Voltage vs. Temperature.

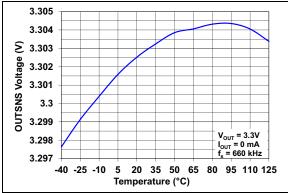

FIGURE 2-8: OUTSNS Voltage vs. Temperature.

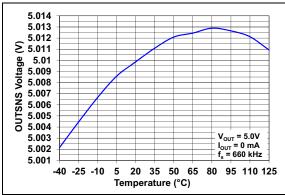

**FIGURE 2-9:** OUTSNS Voltage vs. Temperature.

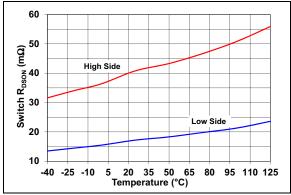

**FIGURE 2-10:**  $R_{DS(on)}$  vs. Temperature.

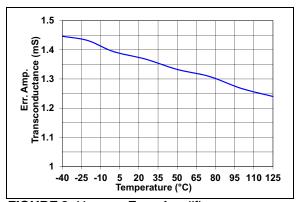

FIGURE 2-11: Error Amplifier Transconductance vs. Temperature.

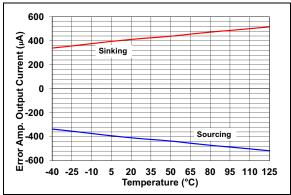

**FIGURE 2-12:** Error Amplifier Output Current vs. Temperature.

### MIC24045

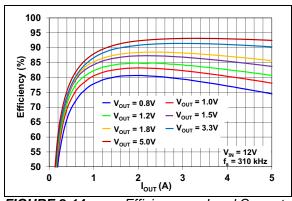

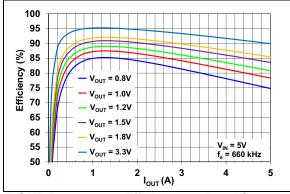

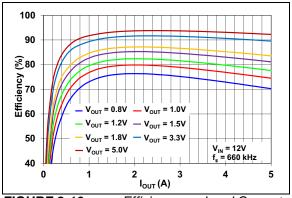

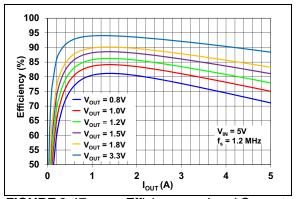

FIGURE 2-13: Efficiency vs. Load Current.

FIGURE 2-14: Efficiency vs. Load Current.

FIGURE 2-15: Efficiency vs. Load Current.

FIGURE 2-16: Efficiency vs. Load Current.

FIGURE 2-17: Efficiency vs. Load Current.

FIGURE 2-18: Efficiency vs. Load Current.

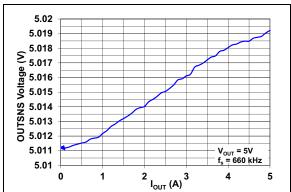

**FIGURE 2-19:** Load Regulation: OUTSNS Voltage vs. I<sub>OUT</sub>.

FIGURE 2-20: Load Regulation: OUTSNS Voltage vs. I<sub>OUT</sub>.

**FIGURE 2-21:** Load Regulation: OUTSNS Voltage vs. I<sub>OUT</sub>.

FIGURE 2-22: Load Regulation: OUTSNS Voltage vs. I<sub>OUT</sub>:

### MIC24045

**Note:** Unless otherwise indicated,  $V_{IN}$  = 12V,  $f_S$  = 660 kHz,  $I_{LIM}$  =  $I_{LIM}$   $L_{S3}$ , L = 2.2  $\mu$ H,  $T_A$  = +25°C.

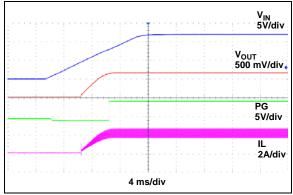

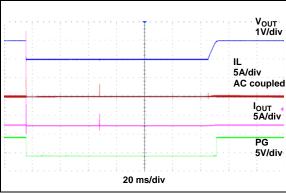

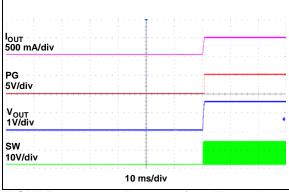

**FIGURE 2-23:**  $V_{IN}$  Turn-on (EN =  $V_{DDA}$ , no  $I^2$ C programming, registers default values for 2Z version),  $R_{LOAD} = 0.3\Omega$ .

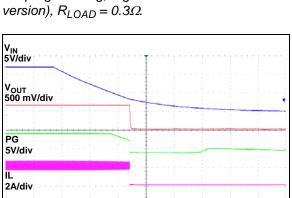

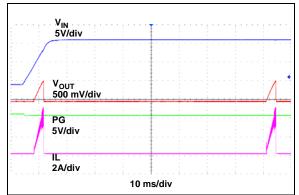

FIGURE 2-24:  $V_{IN}$  Turn-off (EN =  $V_{DDA}$ ),  $R_{LOAD} = 0.3\Omega$ .

4 ms/div

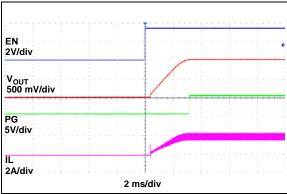

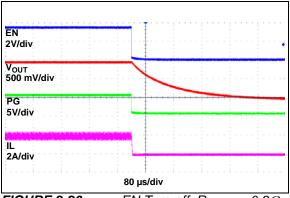

**FIGURE 2-25:** EN Turn-on,  $R_{LOAD} = 0.3\Omega$ .

**FIGURE 2-26:** EN Turn-off,  $R_{LOAD} = 0.3\Omega$ .

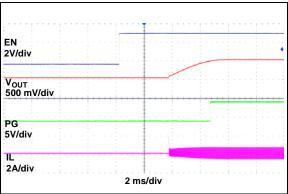

**FIGURE 2-27:** EN Turn-on into pre-biased output  $(V_{pre-bias} = 0.5V)$ .

**FIGURE 2-28:** EN Turn-on into pre-biased output  $(V_{pre-bias} = 0.8V)$ .

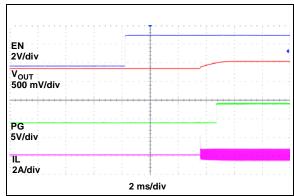

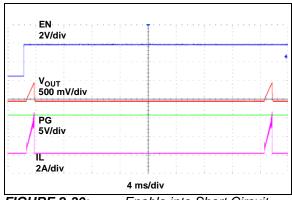

**FIGURE 2-29:** Power-up into Short Circuit,  $(EN = V_{DDA}, \text{ no } l^2C$  programming, registers default values for 2Z version).

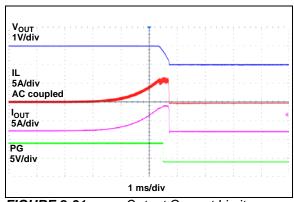

**FIGURE 2-32:** Hiccup Mode Short Circuit Current Limit Response.

FIGURE 2-30: Enable into Short Circuit.

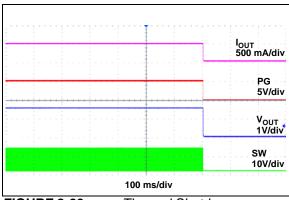

FIGURE 2-33: Thermal Shutdown Response.

FIGURE 2-31: Output Current Limit Threshold.

FIGURE 2-34: Recovery from Thermal Shutdown.

### MIC24045

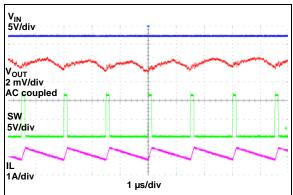

**FIGURE 2-35:** Switching Waveforms -  $f_S = 660 \text{ kHz}$ ,  $I_{OUT} = 0A$ .

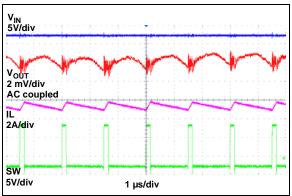

**FIGURE 2-36:** Switching Waveforms -  $f_S = 660 \text{ kHz}$ ,  $I_{OUT} = 5A$ .

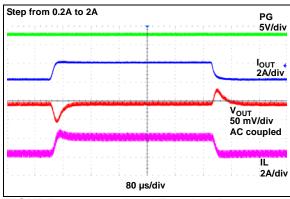

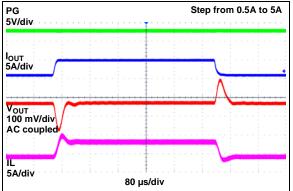

**FIGURE 2-37:** Load Transient Response with  $I_{LIM} = I_{LIM\_LSO}$ .

**FIGURE 2-38:** Load Transient Response with  $I_{LIM} = I_{LIM}$  LS3.

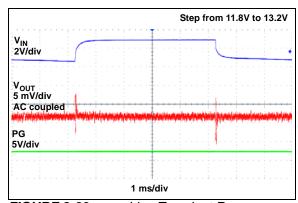

FIGURE 2-39: Line Transient Response.

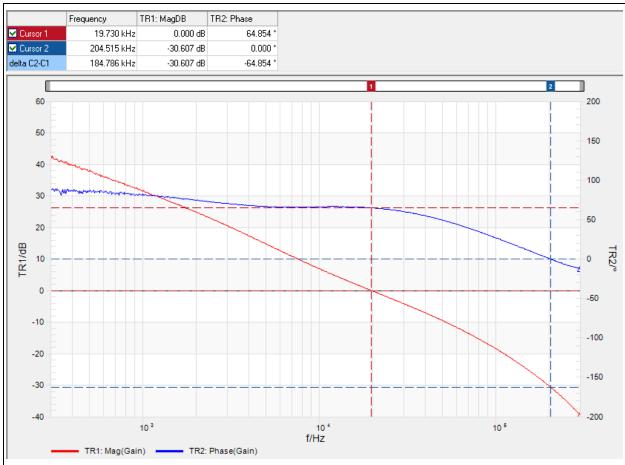

FIGURE 2-40: Voltage Loop Gain Bode Plot,  $V_{OUT}$  = 1.8V,  $f_s$  = 570 kHz, L = 1.2 μH,  $C_{OUT}$  = 266 μF,  $R_{C1}$  = 2.55kΩ,  $C_{C1}$  = 10nF,  $C_{C2}$  = 47pF (see Section 7.7, Compensation Design).

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MIC24045 | Symbol               | Pin Function                                                                                                  |  |

|----------|----------------------|---------------------------------------------------------------------------------------------------------------|--|

| 1, 2     | V <sub>IN</sub>      | Input Voltage Pin                                                                                             |  |

| 3, 4, 13 | $P_{GND}$            | Power Ground Pin                                                                                              |  |

| 5, 6     | LX                   | Switch Node Pin                                                                                               |  |

| 7        | BST                  | Bootstrap Capacitor Pin. A bootstrap capacitor is connected between the BST and LX pins.                      |  |

| 8        | PG                   | Power Good Open-Drain Output Pin                                                                              |  |

| 9        | ADR0                 | I <sup>2</sup> C Address Programming Pin 0                                                                    |  |

| 10       | ADR1                 | I <sup>2</sup> C Address Programming Pin 1                                                                    |  |

| 11       | SCL                  | I <sup>2</sup> C Clock Input Pin                                                                              |  |

| 12       | SDA                  | I <sup>2</sup> C Data Input/Output Pin                                                                        |  |

| 14       | A <sub>GND</sub>     | Analog Ground Pin                                                                                             |  |

| 15       | COMP                 | Transconductance Error Amplifier Output Pin. Connect the compensation network from COMP to A <sub>GND</sub> . |  |

| 16       | OUTSNS               | Output Sensing Pin                                                                                            |  |

| 17       | EN                   | Precision Enable Input Pin                                                                                    |  |

| 18       | $V_{\mathrm{DDA}}$   | Internal Regulator Output Pin                                                                                 |  |

| 19       | $V_{\mathrm{DDP}}$   | MOSFET Drivers Internal Supply Pin                                                                            |  |

| 20       | V <sub>INLDO</sub>   | Internal Regulator Input Pin                                                                                  |  |

| 21       | V <sub>IN</sub> _EP  | V <sub>IN</sub> Exposed Pad. Electrically connected to V <sub>IN</sub> .                                      |  |

| 22       | P <sub>GND</sub> _EP | P <sub>GND</sub> Exposed Pad. Electrically connected to P <sub>GND</sub> .                                    |  |

| 23       | LX_EP                | LX Exposed Pad. Electrically connected to LX.                                                                 |  |

#### 3.1 Input Voltage Pin (V<sub>IN</sub>)

Input Voltage pin for the Buck converter power stage. These pins are the drain terminal of the internal high-side N-channel MOSFET. A 10  $\mu F$  minimum ceramic capacitor should be connected from  $V_{IN}$  to the  $P_{GND}$  pins as close as possible to the device. A combination of multiple ceramic capacitors of different sizes is recommended.

#### 3.2 Power Ground Pin (P<sub>GND</sub>)

Low-side MOSFET source terminal and low-side driver return. Connect the ceramic input capacitors to  $P_{\mbox{\footnotesize{GND}}}$  as close as possible to the device.

#### 3.3 Switch Node Pin (LX)

Drain (low-side MOSFET) and source (high-side MOSFET) connection of the internal power N-channel FETs. The external inductor (switched side) and bootstrap capacitor (bottom terminal) must be connected to these pins.

#### 3.4 Bootstrap Capacitor Pin (BST)

Supply voltage for the driver of the high-side N-channel power MOSFET. Connect the bootstrap capacitor (top terminal) to this pin.

#### 3.5 Power Good Output Pin (PG)

When the output voltage is within 92.5% of the nominal set point, this pin will go from logic low to logic high through an external pull-up resistor. This pin is the drain connection of an internal N-channel FET.

# 3.6 I<sup>2</sup>C Address Programming Pin 0 (ADR0)

Three-state pin (low, high and high-Z) for I<sup>2</sup>C address programming. Together with ADR1, ADR0 defines nine logic values corresponding to nine I<sup>2</sup>C addresses.

# 3.7 I<sup>2</sup>C Address Programming Pin 1 (ADR1)

Three-state pin (low, high and high-Z) for I<sup>2</sup>C address programming. Together with ADR0, ADR1 defines nine logic values corresponding to nine I<sup>2</sup>C addresses.

#### 3.8 I<sup>2</sup>C Clock Input Pin (SCL)

The SCL pin is the serial interfaces Serial Clock pin. This pin is connected to the Host Controllers SCL pin.

The MIC24045 is a slave device, so its SCL pin accepts only external clock signals.

#### 3.9 I<sup>2</sup>C Data Input/Output Pin (SDA)

The SDA pin is the serial interface Serial Data pin. This pin is connected to the Host Controllers SDA pin. The SDA pin has an open-drain N-channel driver.

#### 3.10 Analog Ground Pin (A<sub>GND</sub>)

This pin is a quiet ground for the analog circuitry of the internal regulator and a return terminal for the external compensation network.

# 3.11 Transconductance Error Amplifier Output Pin (COMP)

Connect a compensation network from this pin to  $A_{\mbox{\footnotesize GND}}.$

#### 3.12 Output Sensing Pin (OUTSNS)

Connect this pin directly to the buck converter output voltage. This pin is the top side terminal of the internal feedback divider.

#### 3.13 Precision Enable Input Pin (EN)

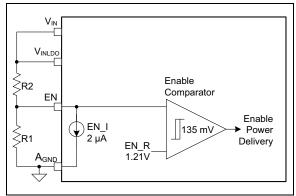

The EN pin is compared to a 1.21V typical threshold to determine the turn-on of the device. After reaching the turn-on threshold, the  $I^2C$ -programmable turn-on delay counter starts. A 2  $\mu A$  (typical) current source pulls down the EN pin to prevent unwanted power delivery in case of a floating EN input. A 135 mV typical hysteresis prevents chattering when power delivery is started.

# 3.14 Internal Regulator Output Pin (V<sub>DDA</sub>)

Output of the internal linear regulator and internal supply for analog control. A 1  $\mu F$  minimum ceramic capacitor should be connected from this pin to  $A_{GND};$  a 2.2  $\mu F$  typical value is recommended.

# 3.15 MOSFET Drivers Internal Supply Pin (V<sub>DDP</sub>)

Internal supply rail for the MOSFET drivers, fed by the  $V_{DDA}$  pin. An internal resistor ( $10\Omega$ ) between the  $V_{DDP}$  and  $V_{DDA}$  pins is provided in the regulator in order to implement an RC filter for switching noise suppression. A 1  $\mu$ F minimum ceramic capacitor should be connected from this pin to  $P_{GND}$ ; a 2.2  $\mu$ F typical value is recommended.

# 3.16 Internal Regulator Input Pin (V<sub>INI DO</sub>)

This pin is typically connected to the input voltage of the buck converter stage ( $V_{IN}$ ). If  $V_{INLDO}$  and  $V_{IN}$  are connected to different voltage rails, individually bypass  $V_{INLDO}$  to ground with a 100 nF ceramic capacitor.

#### 3.17 P<sub>GND</sub> Exposed Pad (P<sub>GND EP</sub>)

Electrically connected to  $P_{GND}$  pins. Connect with thermal vias to the ground plane to ensure adequate heat-sinking. See Section 9.0 "Packaging Information".

#### 3.18 V<sub>IN</sub> Exposed Pad (V<sub>IN EX</sub>)

Electrically connected to  $V_{\text{IN}}$  pins. If an input power distribution plane is available, connect with thermal vias to that plane to improve heat-sinking. See **Section 9.0** "Packaging Information".

#### 3.19 LX Exposed Pad (LX\_EP)

Electrically connected to LX pins. See **Section 9.0** "Packaging Information".

#### 4.0 FUNCTIONAL DESCRIPTION

The MIC24045 is a digitally programmable, 5A valley current-mode controlled regulator featuring an input voltage range from 4.5V to 19V.

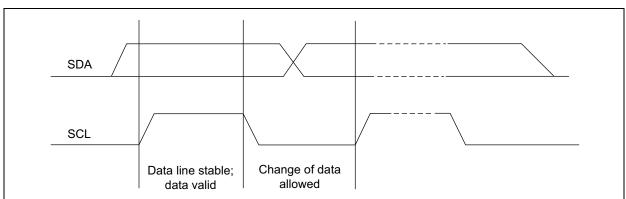

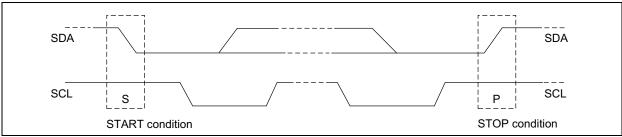

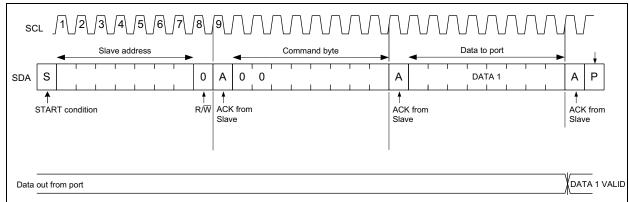

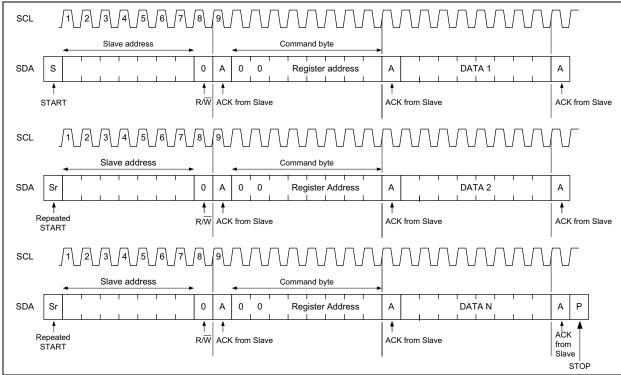

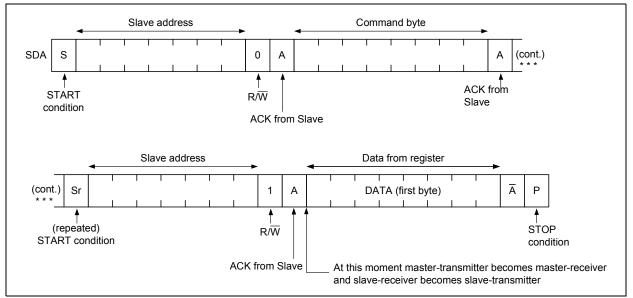

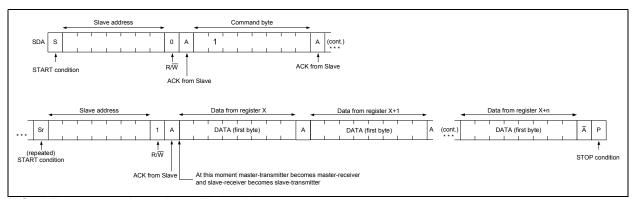

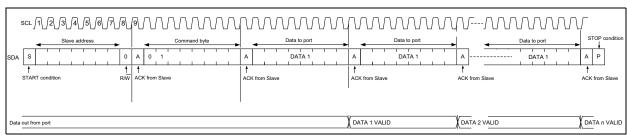

Programmability is achieved by means of an I<sup>2</sup>C-compatible serial digital interface, which can support Serial Clock (SCL) rates up to 400 kHz (Fast mode).

The MIC24045 requires a minimal amount of external components. Only the inductor, supply decoupling capacitors and compensation network are external. The flexibility in the external compensation design allows the user to optimize their design across the entire range of operating parameters such as input voltage, output voltage, switching frequency and load current.

#### 4.1 Theory of Operation

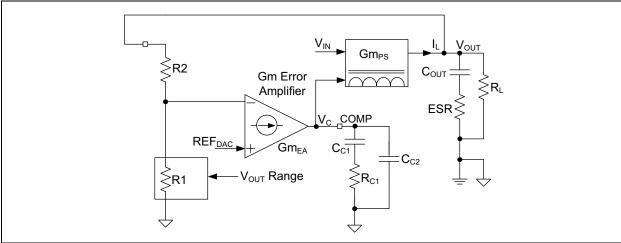

Valley current-mode control is a fixed-frequency, leading-edge-modulated PWM current-mode control. Differing from Peak Current mode, in valley current-mode the clock marks the turn-off of the high-side switch. Upon this instant, the MIC24045 low-side switch current level is compared against the reference current signal from the error amplifier. When the falling low-side switch current signal drops below the current reference signal, the high-side switch is turned on. As a result, the inductor valley current is regulated to a level dictated by the output of the error amplifier.

As shown in Section 7.7 "Compensation Design", the feedback loop includes an internal programmable reference (REF<sub>DAC</sub>) and an output voltage sensing attenuator (R2/R1), which removes the need for external feedback components and improves regulation accuracy. Output voltage feedback is achieved by connecting OUTSNS directly to the output. The high-performance transconductance error amplifier drives an external compensation network at the COMP pin. The COMP pin voltage represents the reference current signal. The COMP pin voltage is fed to the valley current-mode modulator, which also adds slope compensation to ensure current-loop stability. Valley current-mode control requires slope compensation at duty cycles less than 50% for current-loop stability. The slope compensation circuit is internal and it is automatically adapted in amplitude depending upon the frequency, output voltage range and voltage differential (V<sub>IN</sub> - V<sub>OUTSNS</sub>). The internal low-R<sub>DS(ON)</sub> power MOSFETs, the associated adaptive gate driver and the internal bootstrap diode complete the power train.

Overcurrent protection and thermal shutdown protect the MIC24045 from faults or abnormal operating conditions.

# 4.2 Internal LDO, Supply Rails (V<sub>IN</sub>, V<sub>INLDO</sub>, V<sub>DDA</sub>, V<sub>DDP</sub>)

$V_{IN}$  pins represent the power train input. These pins are the drain connection of the internal high-side MOSFET and should be bypassed to  $P_{GND}$  with a X5R or X7R 10  $\mu F$  (minimum) ceramic capacitor, placed as close as possible to the device. A combination of ceramic capacitors of different sizes is recommended.

An internal LDO (biased through  $V_{INLDO}$  pin) provides a clean supply (5.1V typical) for the analog circuits and the I<sup>2</sup>C interface at pin  $V_{DDA}$ . The internal LDO is typically powered from the same power rail feed at  $V_{IN}$ ; however,  $V_{INLDO}$  can also be higher or lower than  $V_{IN}$  and can be connected to any other voltage within its recommended limits.  $V_{INLDO}$  and  $V_{DDA}$  should be locally bypassed (see **Section 3.0 "Pin Description"**). A small series resistor (typically  $2\Omega$ - $10\Omega$ ) can be used in combination with the  $V_{INLDO}$  bypass capacitor to implement a RC filter for suppression of large high-frequency switching noise.

The internal LDO is always enabled and regulation takes place as soon as enough voltage has established between the  $V_{\rm INLDO}$  and  $V_{\rm DDA}$  pins. If an external 5V±10% is available, it is possible to bypass the internal LDO by connecting  $V_{\rm INLDO},\ V_{\rm DDA}$  and  $V_{\rm DDP}$  together at the external 5V rail, thus improving overall efficiency.

The MIC24045 does not require a separate supply for the  $I^2C$  interface and for the internal logic registers, which are all powered from the  $V_{DDA}$  rail. An internal Undervoltage Lock-Out circuit (UVLO) monitors the level of  $V_{DDA}$  and resets the interface and the internal registers if the  $V_{DDA}$  voltage is below the UVLO threshold.

$V_{DDP}$  is the power supply rail for the gate drivers and bootstrap circuit. This pin is subject to high-current spike with high-frequency content. To prevent these from polluting the analog  $V_{DDA}$  supply, a separate capacitor is needed for  $V_{DDP}$  pin bypassing. An internal  $10\Omega$  resistor is provided between pins  $V_{DDA}$  and  $V_{DDP}$ , allowing a switching noise attenuation RC filter with the minimum amount of external components to be implemented. It is possible, although typically not necessary, to lower the RC time constant by connecting an external resistor between pins  $V_{DDA}$  and  $V_{DDP}$

#### 4.3 Enable (EN)

The EN pin starts/stops the power delivery to the output. It does not turn off the internal LDO. The EN pin does not act as a Reset signal for the  $I^2C$  registers, only the  $V_{DDA}$  UVLO circuit does.

Rising threshold is a precise 1.21V±70 mV. A 135 mV typical hysteresis prevents chattering due to switching noise and/or slow edges. A 2  $\mu\text{A}$  typical pull-down current with ±1  $\mu\text{A}$  accuracy prevents unwanted start-ups if the EN pin is momentarily floating. To achieve automatic turn-on as soon as enough voltage is present, connect EN to  $V_{DDA}$ .

#### 4.4 Power Good (PG)

PG is an open-drain output. For asserting a logic HIGH level, PG requires an external resistor connected to a pull-up voltage (V<sub>PU\_PG</sub>), which should not exceed 5.5V.

PG is asserted with a typical delay of 0.45 ms when the output voltage (OUTSNS) reaches 92.5% of its target regulation voltage. PG is de-asserted with a typical delay of 80 µs when the output voltage falls below 90% of its target regulation voltage. The PG falling delay acts as a de-glitch timer against very short spikes. The PG output is always immediately de-asserted when the EN pin is below the power delivery enable threshold (EN\_R/EN\_F). The pull-up resistor should be large enough to limit the PG pin current to below 2 mA. The PG is in a defined state once the V<sub>DDA</sub> voltage is greater than about 1V, but with reduced current sinking capability.

The PG is also immediately de-asserted (with no delay) whenever an undervoltage condition on  $V_{DDA}$  is detected, or in thermal shutdown.

#### 4.5 Inductor (LX) and Bootstrap (BST)

The external inductor is connected to LX. The high-side MOSFET driver circuit is powered between BST and LX by means of an external capacitor (typically 100 nF) that is replenished from rail  $V_{DDP}$  during the low-side MOSFET ON-time. The bootstrap diode is internal.

# 4.6 Output Sensing (OUTSNS) and Compensation (COMP)

OUTSNS should be connected exactly to the desired point-of-load regulation, avoiding parasitic resistive drops. The impedance seen into OUTSNS is high (tens of  $k\Omega$  or more, depending on the selected output voltage value), therefore its loading effect is typically negligible. OUTSNS is also used by the slope compensation generator.

COMP is the connection for the external compensation network. COMP is driven by the output of the transconductance error amplifier. Care must be taken to return the compensation network ground directly to A<sub>GND</sub>.

#### 4.7 Soft-Start

The MIC24045 features four different I<sup>2</sup>C-selectable soft-start slew-rate values (0.16V/ms, 0.38V/ms, 0.76V/ms and 1.5V/ms). See the section **Section 5.0** "Registers Maps and I2C Programmability" for the value vs. code mapping. The internal reference is ramped up at the selected rate. Note that this is the internal reference soft-start slew rate and that the actual slew rate seen at the output should take into account the internal divider attenuation, as detailed in the **Section 7.0** "Application Information".

#### 4.8 Start-Up Delay

The MIC24045 features eight different I<sup>2</sup>C-selectable start-up delays (from 0 ms to 10 ms). These represent the added delays from the EN rising edge to the beginning of the power delivery (soft-start). See the section **Section 5.0**, **Registers Maps and I2C Programmability** for the value vs. code mapping.

#### 4.9 Switching Frequency

The MIC24045 features eight different I $^2$ C-selectable switching frequencies from 310 kHz to 1200 kHz. See Section 5.0 "Registers Maps and I2C Programmability" for the value vs. code mapping. Also pay attention to voltage conversion ratio limitations due to minimum  $T_{ON}$  and  $T_{OFF}$ , as stated in Section 7.0 "Application Information".

#### 4.10 Pre-Biased Output Start-Up

The MIC24045 is designed to achieve safe start-up into a pre-biased output without discharging the output capacitors.

### 4.11 Thermal Warning and Thermal Shutdown

The MIC24045 has a thermal shutdown protection that prevents operation at excessive temperature. The thermal shutdown threshold is typically set at +160°C with a hysteresis of +25°C.

The MIC24045 features a Thermal Warning flag that is readable through the  $I^2C$  interface (register polling is needed). The Thermal Warning flag signals the approaching of thermal shutdown, so that appropriate system-level countermeasures can be undertaken.

Note that a thermal shutdown event will not disable the internal  $V_{DDA}$  linear regulator, but only the power stage. In this way, the  $I^2C$  interface remains powered and can still be read throughout the duration of the thermal shutdown.

#### 4.12 Overcurrent Protection

The MIC24045 features instantaneous cycle-by-cycle current limit with current sensing both on the low-side and high-side switches. It also offers a Hiccup mode for prolonged overloads or short-circuit conditions.

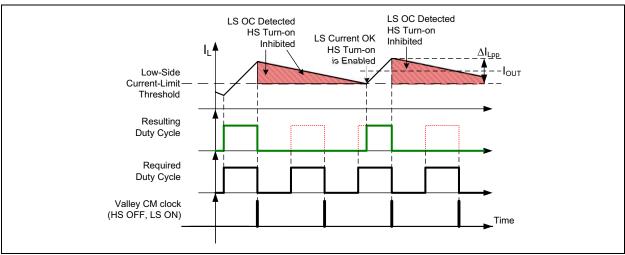

Low-side cycle-by-cycle protection detects the current level of the inductor current during the low-side MOS-FET ON time. The high-side MOSFET turn-on is inhibited as long as the low-side MOSFET current limit is above the low-side current-limit threshold level. The inductor current will continue decaying until the current falls below the threshold, then the high-side MOSFET will be enabled again according to the duty cycle requirement from the PWM modulator.

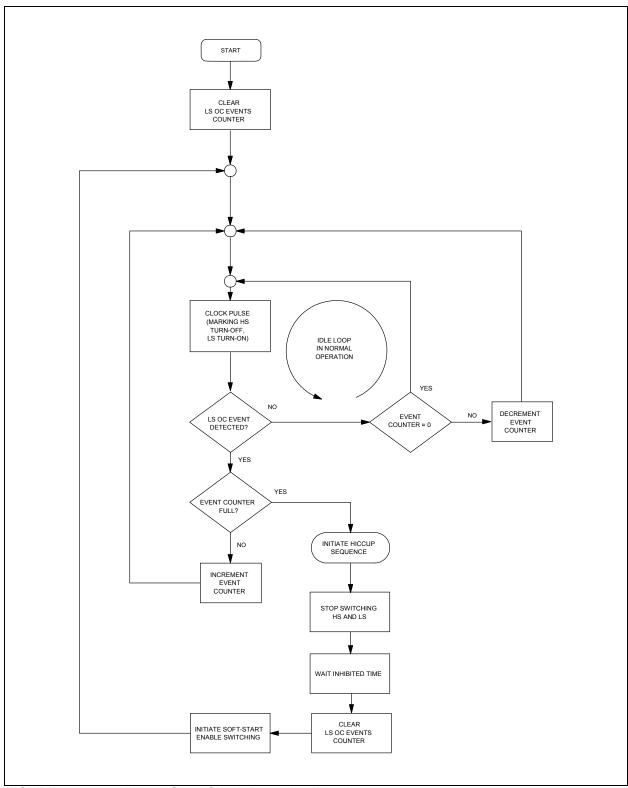

The mechanism is illustrated in Figure 4-1.

FIGURE 4-1: Low-Side Cycle-by-Cycle Current-Limit Action.

The low-side current limit is programmable at four different levels (for 2A, 3A, 4A and 5A loads) in order to optimize inductor size for different application requirements. These levels are listed in **Section 5.0** "Registers Maps and I2C Programmability".

Since the low-side current limit acts on the valley current, the DC output current level ( $I_{OUT}$ ), where the low-side cycle-by-cycle current limit is engaged, will be higher than the current limit value by an amount equal to  $\Delta IL_{PP}/2$ , where  $\Delta IL_{PP}$  is the peak-to-peak inductor ripple current.

The high-side current limit is approximately 1.4-1.5 times greater than the low-side current limit (typical values). The high-side cycle-by-cycle current limit immediately truncates the high-side ON time without waiting for the OFF clocking event.

A leading edge blanking (LEB) timer (108 ns, typical) is provided on the high-side cycle-by-cycle current limit to mask the switching noise and to prevent falsely triggering the protection. High-side cycle-by-cycle current limit action cannot take place before the LEB timer expires.

Hiccup mode protection reduces power dissipation in permanent short-circuit conditions. On each clock cycle, where a low-side cycle-by-cycle current-limit event is detected, a 4-bit up/down counter is incremented. On each clock cycle, without a concurrent low-side current limit event, the counter is decremented or left at zero. The counter cannot wrap-around below

0000 and above 1111. High-side current limit events do not increment the counter. Only detections from low-side current limit events trigger the counter.

If the counter reaches 1111 (or 15 events), the high and low-side MOSFETs become tri-stated and power delivery to the output is inhibited for a duration which is dependent on the soft-start rate and can be calculated with the following equation:

#### **EQUATION 4-1:**

$$Inhibited \ Time = \frac{13.5 V}{SS\_SRx}$$

Where

$$SS\_SRx = selected \ soft-start \ rate \\ (SS\_SRx = SS\_SR0, SS\_SR1, SS\_SR2 \\ or \ SS\_SR3). \\ See \ Electrical \ Characteristics \ table.$$

This digital integration mechanism provides immunity to the momentary overloading of the output. After the wait time, the MIC24045 retries entering operation and initiates a new soft-start sequence.

Note that Hiccup mode short-circuit protection is active at all times, including the soft-start ramp. In case of very large output capacitors, consider slowing down the soft-start slew rate to prevent start-up problems, especially if the load is completely discharging the output capacitor during the hiccup wait time.

FIGURE 4-2: Hiccup Short-Circuit Protection Flowchart.

# 5.0 REGISTERS MAPS AND I<sup>2</sup>C PROGRAMMABILITY

The MIC24045 internal registers are summarized in Table 5-1, below.

TABLE 5-1: MIC24045 REGISTER MAP

| Register<br>Address | Register<br>Name | Туре | В7       | В6       | B5       | B4       | В3       | B2       | B1       | В0       |

|---------------------|------------------|------|----------|----------|----------|----------|----------|----------|----------|----------|

| 0h                  | Status           | RO   | OCF      | ThSDF    | ThWrnF   | Reserved | EnS      | Reserved | Reserved | PGS      |

| 1h                  | Setting 1        | RW   | ILIM1    | ILIM0    | Freq2    | Freq1    | Freq0    | Reserved | Reserved | Reserved |

| 2h                  | Setting 2        | RW   | Reserved | SUDIy2   | SUDly1   | SUDIy0   | Mrg1     | Mrg0     | SS1      | SS0      |

| 3h                  | VOUT             | RW   | VOUT7    | VOUT6    | VOUT5    | VOUT4    | VOUT3    | VOUT2    | VOUT1    | VOUT0    |

| 4h                  | Command          | RW   | Reserved | CIFF     |

#### 5.1 STATUS Register

In the read-only STATUS registers, diagnostic information is provided. Bits can be F = latched (Flag) or S = non-latched (Status).

Flag bits are set when the corresponding Fault condition has occurred and do not return-to-zero once the Fault condition has ceased. Flags can only be cleared by writing '1' in Bit 0 of the COMMAND register 4h, or

by power cycling. Status bits are set when the corresponding Fault condition has occurred and return to zero automatically once the Fault condition has ceased.

Default bits value at power-up is zero, except for Bit 2 (which will always be read as '1') and Bit 1, which is '1' if no Fault conditions are detected.

#### REGISTER 5-1: STATUS – STATUS REGISTER (ADDRESS 0h)

| R-0   | R-0   | R-0    | R'0'     | R-0 | R'1'     | R-1      | R-0   |

|-------|-------|--------|----------|-----|----------|----------|-------|

| OCF   | ThSDF | ThWrnF | Reserved | EnS | Reserved | Reserved | PGS   |

| bit 7 |       |        |          |     |          |          | bit 0 |

Legend:

R = Readable bit

W = Writable bit

U = Unimplemented bit, read as '0'

-n = Value at POR

'1' = Bit is set

'0' = Bit is cleared

x = Bit is unknown

RC = Read-then-clear bit

bit 7 OCF: Over-Current Flag bit. OCF is set high whenever an over-current event occurs. Latched. bit 6 **ThSDF:** Thermal Shut-down Flag bit. ThSDF is set high whenever a Thermal Shutdown occurs. Latched. bit 5 ThWrnF: Thermal Warning Flag bit. ThWrnF is set high whenever a Thermal Warning occurs. Latched. bit 4 **Reserved:** Flag bit. Always read as zero. bit 3 EnS: Enable Pin Status bit. EnS reflects the logic value present on pin EN. Non-latched. bit 2 Reserved: Status bit. Always read as '1'. bit 1 Reserved: Default status at POR is '1' (no faults detected). bit 0 PGS: Power-Good Status bit. PGS reflects the logic value present on pin PG. Non-latched.

#### REGISTER 5-2: SETTING 1 – SETTING 1 REGISTER (ADDRESS 1h)

| RW-V  | RW-V  | RW-V  | RW-V  | RW-V  | U-0      | U-0      | U-0      |

|-------|-------|-------|-------|-------|----------|----------|----------|

| ILIM1 | ILIM0 | Freq2 | Freq1 | Freq0 | Reserved | Reserved | Reserved |

| bit 7 |       |       |       |       |          |          | bit 0    |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

RC = Read-then-clear bit  $V = factory-programmed POR value^{(1)}$

- Note 1: Default Status settings at power-up can be changed at the factory. Standard selections are described in Section 6.0 "MIC24045 Default Settings Values at Power-Up". Overwriting default settings by I<sup>2</sup>C has no permanent effect and values will return to factory default values upon power cycling.

- 2: Changing Setting 1 Register values while power delivery is enabled is not recommended. To change settings by I<sup>2</sup>C, set EN pin low first, then write the new configuration, and finally, set EN pin high again to resume power delivery.

#### REGISTER 5-2: SETTING 1 – SETTING 1 REGISTER (ADDRESS 1h) (CONTINUED)

bit 7-6 **ILIM<1:0>:** MOSFET Current Limit bit. See the Current Limit selection in table below:

| ILIM1 | ILIMO | TYP Low-Side<br>Current Limit (A) | TYP High-Side<br>Current Limit (A) | Nominal Load<br>Current (A) |

|-------|-------|-----------------------------------|------------------------------------|-----------------------------|

| 0     | 0     | 3.25                              | 4.7                                | 2                           |

| 0     | 1     | 4.3                               | 6.2                                | 3                           |

| 1     | 0     | 5.6                               | 8.6                                | 4                           |

| 1     | 1     | 6.2                               | 9.4                                | 5                           |

bit 5-3 Freq0 (Switching Frequency): See the Switching Frequency selection in table below:

| Freq2 | Freq1 | Freq0 | Frequency<br>(kHz) |

|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 310                |

| 0     | 0     | 1     | 400                |

| 0     | 1     | 0     | 500                |

| 0     | 1     | 1     | 570                |

| 1     | 0     | 0     | 660                |

| 1     | 0     | 1     | 780                |

| 1     | 1     | 0     | 970                |

| 1     | 1     | 1     | 1200               |

bit 2-0 Reserved: Unimplemented bit. Read as '0'.

- Note 1: Default Status settings at power-up can be changed at the factory. Standard selections are described in Section 6.0 "MIC24045 Default Settings Values at Power-Up". Overwriting default settings by I<sup>2</sup>C has no permanent effect and values will return to factory default values upon power cycling.

- 2: Changing Setting 1 Register values while power delivery is enabled is not recommended. To change settings by I<sup>2</sup>C, set EN pin low first, then write the new configuration, and finally, set EN pin high again to resume power delivery.

#### REGISTER 5-3: SETTING 2 – SETTING 2 REGISTER (ADDRESS 2h)

| U-0      | RW-V   | RW-V   | RW-V   | RW-0 | RW-0 | RW-V | RW-V  |

|----------|--------|--------|--------|------|------|------|-------|

| Reserved | SUDly2 | SUDly1 | SUDIy0 | Mrg1 | Mrg0 | SS1  | SS0   |

| bit 7    |        |        |        |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

RC = Read-then-clear bit  $V = factory-programmed POR value^{(1)}$

bit 7 Reserved: Unimplemented bit. Read as '0'. Writing to this bit has no effect.

bit 6-4 **SUDly<2:0>:** Start-Up Delay bit. Delay to start power delivery from the rising edge of the EN signal. See the Start-up Delay selection in table below:

| SUDIy2 | SUDIy1 | SUDIy0 | Start-Up Delay (ms) |

|--------|--------|--------|---------------------|

| 0      | 0      | 0      | 0                   |

| 0      | 0      | 1      | 0.5                 |

| 0      | 1      | 0      | 1                   |

| 0      | 1      | 1      | 2                   |

| 1      | 0      | 0      | 4                   |

| 1      | 0      | 1      | 6                   |

| 1      | 1      | 0      | 8                   |

| 1      | 1      | 1      | 10                  |

bit 3-2 **Mrg<1:0>:** Voltage Margins bit. These bits can be changed at any time during power delivery. See the Voltage Margining selection in table below:

| Mrg1 | Mrg0 | Change to nominal V <sub>OUT</sub> Setting (%) |

|------|------|------------------------------------------------|

| 0    | 0    | 0%                                             |

| 0    | 1    | -5%                                            |

| 1    | 0    | +5%                                            |

| 1    | 1    | +5%                                            |

Default at power-up is <0:0>

bit 1-0 **SS1<1:0>:** Soft-Start Ramp Rate bit. See the Soft-Start Tamp Rates selection in table below:

| SS1 | SS0 | Soft-Start Slope (V/ms) |

|-----|-----|-------------------------|

| 0   | 0   | 0.16                    |

| 0   | 1   | 0.38                    |

| 1   | 0   | 0.76                    |

| 1   | 1   | 1.5                     |

- Note 1: For all bits (except Margining bits Mrg<1:0>) the Default Status at power-up can be changed at the factory. Standard selections are described in Section 6.0 "MIC24045 Default Settings Values at Power-Up". Overwriting default settings by I<sup>2</sup>C has no permanent effect and values will return to factory default settings upon power cycling. Default power-up status for Mrg<1:0> is <0:0>.

- 2: With the exception of Margining Bits Mrg<1:0>, changing Setting 2 register values while power delivery is enabled is not recommended. To change settings by I<sup>2</sup>C, set EN pin low first, then write the new configuration, and finally, set EN pin high again to resume power delivery.

#### REGISTER 5-4: VOUT – VOUT REGISTER (ADDRESS 3h)

| RW-V  |

|-------|-------|-------|-------|-------|-------|-------|-------|

| VOUT7 | VOUT6 | VOUT5 | VOUT4 | VOUT3 | VOUT2 | VOUT1 | VOUT0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

RC = Read-then-clear bit  $V = factory-programmed POR value^{(1)}$

- bit 7-0 **VOUT<7:0>:** VOUT register bits can be changed at any time during power delivery, provided that transitions from one code to another:

- are done step-by-step, by small VOUT increments. The speed of the transition is left to the user and limited by the I<sup>2</sup>C writing interface speed.

- code transition shall take place only within the same VOUT Range. Crossing boundaries of resolution ranges may cause VOUT glitches and it is not recommended.

See VOUT selection in table below:

| <b>VOUT Range</b> | Step Size | Codes-decimal (hex)    |

|-------------------|-----------|------------------------|

| 0.640V to 1.280V  | 5 mV      | 0 (00h) to 128 (80h)   |

| 1.290V to 1.950V  | 10 mV     | 129 (81h) to 195 (C3h) |

| 1.980V to 3.420V  | 30 mV     | 196 (C4h) to 244 (F4h) |

| 4.750V to 5.250V  | 50 mV     | 245 (F5h) to 255 (FFh) |

- Note 1: Default Status settings at power-up can be changed at the factory. Standard selections are described in Section 6.0 "MIC24045 Default Settings Values at Power-Up". Overwriting default settings by I<sup>2</sup>C has no permanent effect and values will return to factory default values upon power cycling.

- 2: The functionality of the MIC24045 at any output voltage selection is subject to limitations described in Section 7.0 "Application Information".

#### REGISTER 5-5: COMMAND - COMMAND REGISTER (ADDRESS 4h)

| RW-0     | RW-0  |

|----------|----------|----------|----------|----------|----------|----------|-------|

| Reserved | CIFF  |

| bit 7    |          |          |          |          |          |          | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

RC = Read-then-clear bit

bit 7-1 Reserved<7:1>: Writing to these bits has no effect to the device operation.

bit 0 **CIFF:** Clear Fault Flags bit. Writing '1' to bit 0 will clear all Fault Flags. The CIFF bit is self-clearing and it returns to '0' as soon as the Fault Flags have been cleared.

# 6.0 MIC24045 DEFAULT SETTINGS VALUES AT POWER-UP

Part number MIC24045-XXYFL also designates different default settings values at power-up, before any I<sup>2</sup>C writing operation takes place. These values are programmed at factory.

Different default settings are obtained by burning an OTP memory (fuses). The **XX** code corresponds to a certain combination of output voltage, switching frequency, nominal load current and soft-start ramp rate. Start-up delay and voltage margining always default to 0 ms and 0%. The blank (all zeros) OTP memory option has a special code (**2Z**).

The standard default settings are as shown in Table 6-1. For availability of other default settings, contact the nearest Microchip Sales Office.

TABLE 6-1: STANDARD DEFAULT SETTINGS

| Full Part Number | Code | V <sub>OUT</sub> (V) | Frequency | Load Current | Reference<br>Soft-Start Rate |

|------------------|------|----------------------|-----------|--------------|------------------------------|

| MIC24045-2ZYFL   | 2Z   | 0.64                 | 310 kHz   | 2A           | 0.16V/ms                     |